面向自动驾驶的CMOS图像传感器与稀疏感知加速器的2.5D/3D集成系统设计与热分析

- 2026-02-28 01:12:36

面向自动驾驶的CMOS图像传感器与稀疏感知加速器的2.5D/3D集成系统设计与热分析

JANAK SHARDA, MADISON MANLEY, ANKIT KAUL, WANTONG LI, MUHANNAD BAKIR, AND SHIMENG YU. Design and Thermal Analysis of 2.5D and 3-D Integrated System of a CMOS Image Sensor and a Sparsity-Aware Accelerator for Autonomous Driving.Digital Object Identifier 10.1109/JEDS.2024.3354621. https://creativecommons.org/licenses/by-nc-nd/4.0/

随着自动驾驶技术的快速发展,深度学习算法在图像处理和目标追踪中的应用日益广泛。CMOS图像传感器(CIS)作为视觉感知的核心器件,需实时采集高分辨率图像并传输至后端处理器进行分析。然而,传统MIPI接口在数据传输过程中存在能耗高、延迟大等问题,难以满足实时性和能效要求。为此,研究者提出采用2.5D/3D先进封装技术将CIS与处理器紧密集成,以缩短互连距离、降低寄生参数,从而显著减少数据移动能耗。然而,这种高密度集成也带来了热耦合问题,可能导致芯片温度升高,影响图像质量和电路性能。因此,开展热感知设计成为实现高效、可靠的集成系统的关键。

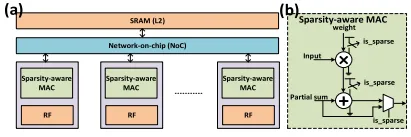

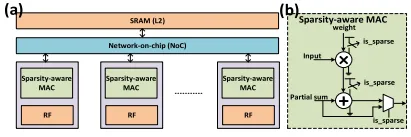

本文在前期研究基础上,设计了一种基于PE阵列的稀疏感知后端加速器,并与3D堆叠的CIS进行2.5D/3D集成,系统评估其在自动驾驶多目标追踪任务中的性能与热特性。后端加速器设计:采用MAESTRO工具设计PE阵列架构,支持kc-p数据流,适配ResNet-50网络。每个PE单元包含稀疏感知的8位MAC运算模块,通过“is_sparse”信号实现权值为0时的功耗门控,显著降低动态功耗。加速器整体包括3.66 MB的L2全局缓冲和局部寄存器文件,支持90%权值稀疏性,模型大小仅为0.34 MB。图1展示了稀疏感知MAC单元的结构,包含乘法器与加法器的功耗门控机制。

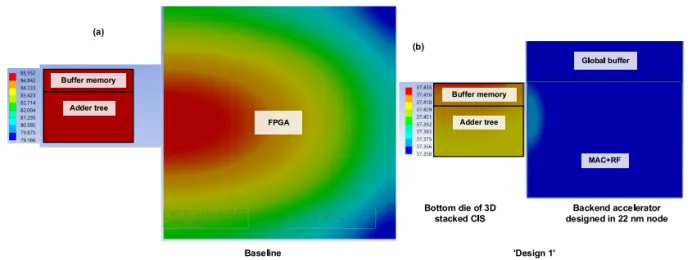

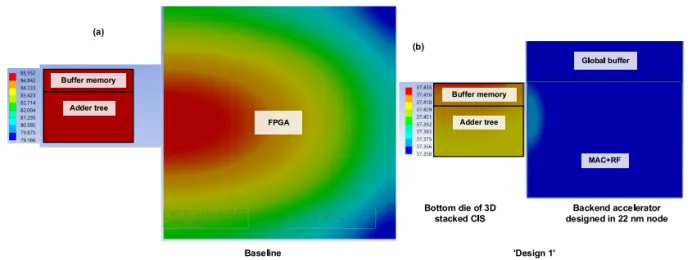

图1. (a) 基于PE阵列的后端加速器示意图。网络结构(NoC)由数据流决定,在本案例中采用文献[11]中的kc-p数据流。(b) 带稀疏感知功能的8b×8b多址接入控制器(MAC)单元,配备功率门控乘法器与加法器。当权重为0时,信号‘is sparse’=1。((a)改编自文献[11]) 2.5D集成与热模拟:将CIS与加速器集成于硅中介层上,建模2.5D互连的RC寄生参数,并在Ansys Mechanical APDL中进行热仿真。结果显示,在22nm工艺下,系统峰值温度仅上升至37.4°C,远低于FPGA方案的84.8°C,图2对比了FPGA与定制加速器在2.5D集成下的热分布图,验证了定制加速器在能效与热控制方面的优势。

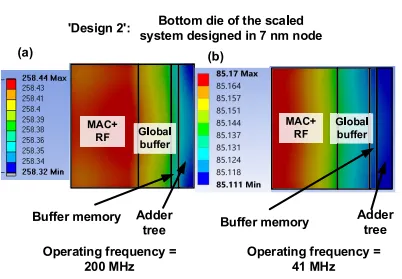

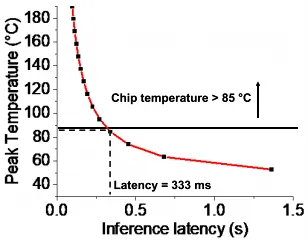

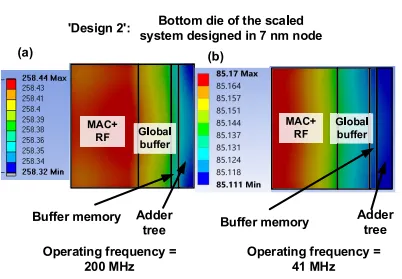

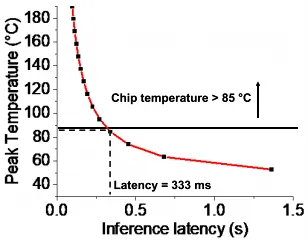

图2. (a) FPGA 与CIS的2.5D集成热图(引自[10])。(b) CIS与定制加速器(“设计1”)的2.5D集成热图。后端加速器采用22纳米工艺节点设计。 3D集成与频率优化:为进一步提升能效,将加速器与NPC引擎共同集成于7nm工艺的单芯片中,形成真正的3D堆叠结构。由于光敏二极管位于顶层且无法加装散热器,热管理成为挑战。仿真表明,在200MHz下运行会导致峰值温度超过250°C。为此,将工作频率降至41MHz,使峰值温度控制在85°C以内,同时满足3 FPS的实时处理要求。图3展示了3D集成在200MHz与41MHz下的热分布图;图4则给出了峰值温度与延迟之间的关系曲线。

图3. (a) CIS与定制加速器(“Design 2”)三维集成的热图。后端加速器与NPC电路采用7纳米工艺节点缩放,并通过铜-铜混合键合在底层集成。工作频率为200 MHz,峰值温度超过250°C。(b) “Design 2”在较低频率41 MHz运行时的热图,其峰值温度为85°C。

图4. 变化工作频率并绘制峰值温度与推理延迟的关系曲线。根据所需工作条件(延迟<333毫秒且峰值温度<85°C),我们选择工作频率为41 MHz。

本研究成功设计并评估了面向自动驾驶的2.5D/3D集成CIS与稀疏感知加速器系统。2.5D集成在22nm工艺下实现了低功耗与低温升,3D集成则在7nm工艺下实现了45.81 TOPS/W的能效,并通过频率调节在热预算内完成多目标追踪任务。未来工作可进一步探索自适应频率调度、异构集成散热结构设计,以及更复杂的神经网络在边缘端的实时部署。该研究为智能感知芯片的集成设计提供了可行的热管理策略与架构参考。

Design and Thermal Analysis of 2.5D and 3-D Integrated System of a CMOS Image Sensor and a Sparsity-Aware Accelerator for .pdf

欢迎关注公众号 “芯片散热” 投稿邮箱:chipheat@163.com

论文信息:

论文链接:

PART1

研究背景

PART2

研究内容

PART3

总结与展望

本文来自网友投稿或网络内容,如有侵犯您的权益请联系我们删除,联系邮箱:wyl860211@qq.com 。